- 您现在的位置:买卖IC网 > Sheet目录3873 > PIC16F884-I/ML (Microchip Technology)IC PIC MCU FLASH 4KX14 44QFN

PIC16F88X

DS80302F-page 12

2009 Microchip Technology Inc.

11. Module: MSSP (SPI Master Mode)

When the MSSP module is configured as a SPI

master with CKP set, (SPI clock idles high)

disabling the module by clearing the SSPEN bit

will cause the clock line to be driven low for 2 TOSC

before the setting of the RC3 output in the PORTC

register takes effect.

Similarly on enabling the module. There is a 1

TOSC period where the clock line will be driven low

before the CKP bit takes effect and the line is

driven high.

Work around

A pull-up resistor on the SCK line allows the pin to

be configured as high-impedance during disabling/

enabling the module and the line to be pulled high

by the resistor.

The TRISC3 bit should be set before disabling or

enabling the module to tristate the pin, and then

cleared before transmission.

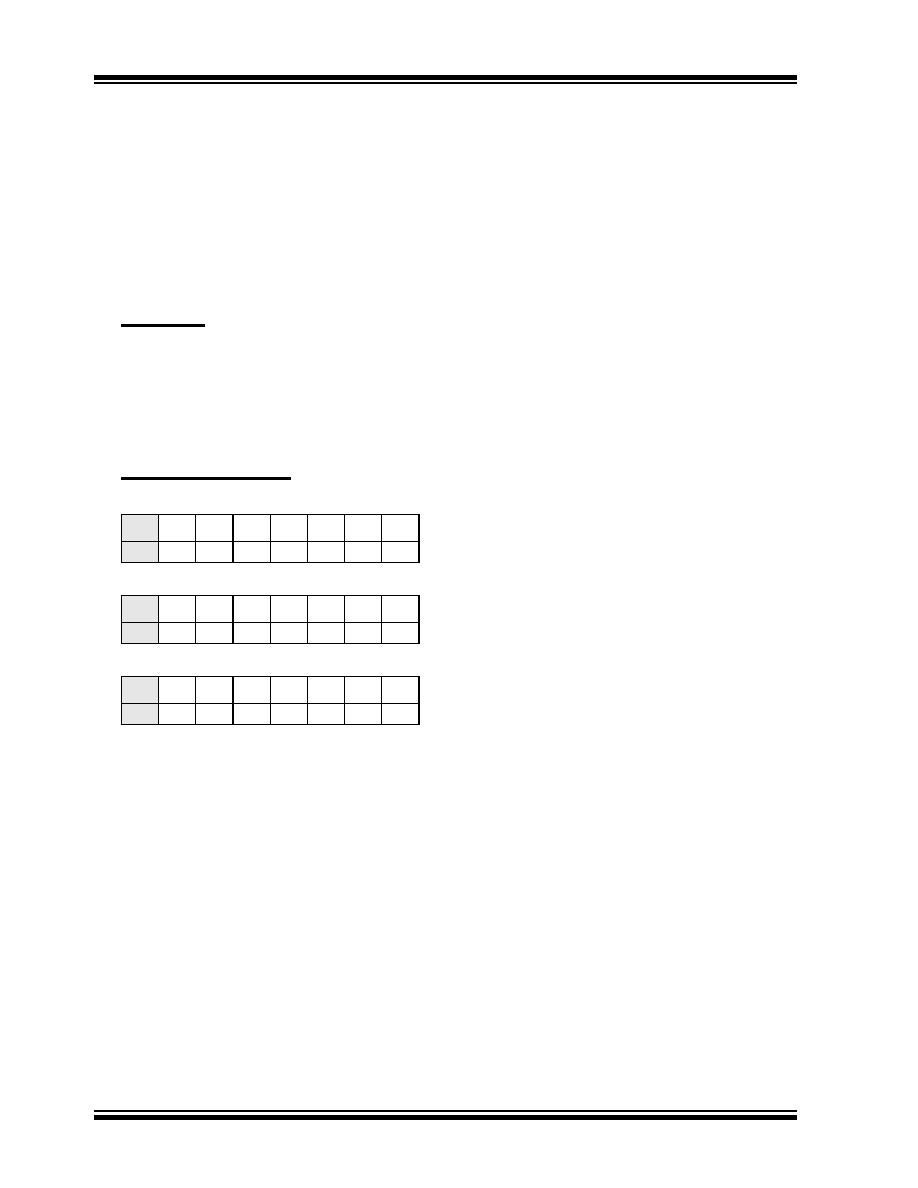

Affected Silicon Revisions

PIC16F882

PIC16F883/PIC16F884

PIC16F886/PIC16F887

A0

X

A0

X

A2

X

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

PIC16CR77-I/P

IC PIC MCU 8KX14 40DIP

PIC18F45K20-I/MV

MCU 32KB FLASH 1536B RAM 40-UQFN

PIC16CR76T-I/SS

IC PIC MCU 8KX14 28SSOP

PIC18F13K50-I/P

IC PIC MCU FLASH 4KX16 20-PDIP

PIC16CR76T-I/SO

IC PIC MCU 8KX14 28SOIC

PIC18LF24K22-I/MV

IC PIC MCU 16KB FLASH 28UQFN

PIC18LF24K22-I/ML

IC PIC MCU 16KB FLASH 28QFN

PIC16CR76T-I/ML

IC PIC MCU 8KX14 28QFN

相关代理商/技术参数

PIC16F884-I/P

功能描述:8位微控制器 -MCU 7KB Flash 256 RAM 36 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16F884-I/PT

功能描述:8位微控制器 -MCU 7KB Flash 256 RAM 36 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16F884T-I/ML

功能描述:8位微控制器 -MCU 7KB Flash 256 RAM 36 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16F884T-I/PT

功能描述:8位微控制器 -MCU 7KB Flash 256 RAM 36 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16F886-E/ML

功能描述:8位微控制器 -MCU 14KB Flash 368 RAM 25 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16F886-E/SO

功能描述:8位微控制器 -MCU 14KB Flash 368 RAM 25 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16F886-E/SP

功能描述:8位微控制器 -MCU 14KB Flash 368 RAM 25 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16F886-E/SP

制造商:Microchip Technology Inc 功能描述:8-Bit Microcontroller IC